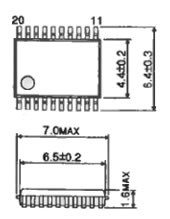

Микросхема TA31273FN, производимая фирмой TOSHIBA, предназначена для построения схемы приемника данных, передаваемых по радиоканалу в пределах 240-450 MHz, с амплитудной модуляцией. Схема супергетеродинная с однократным преобразованием частоты. Промежуточная частота 10.7 МГц. Гетеродин внешний, причем, частота гетеродина должна быть в 8 раз ниже необходимой.

В микросхеме есть умножитель частоты на 8, пройдя через который сигнал гетеродине, уже восьмикратной частоты, поступает на смеситель Умножитель частоты на 8 может быть отключен подачей логического нуля на вывод 3. Стабилизация частоты гетеродина может быть кварцевой или с помощью синтезатора частоты.

В энергосберегающий режим микросхему переводят подачей логического нуля на вывод 17

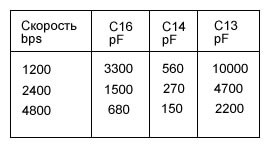

Параметры элементов фильтра для различных скоростей приема данных приведены в таблице.

Некоторые параметры:

Некоторые параметры:1. Напряжение питания (Vcc) 3...5.5V (номинальное значение 5V)

2. Входная частота 240...450 MHz.

3. Номинальный ток потребления 6,8mA.

4. Ток потребления в энергосберегающем режиме (0 на выв 17) не более 5mА

5. Коэффициент передачи УРЧ ....... 20 dB

6. Входное сопротивление УРЧ 900 Оm

7. Входная емкость УРЧ ........ 2.5pF

8. Выходная емкость УРЧ ........ 2 pF

9. Коэффициент передачи смесителя.....17.5. 25.5 dB

10. Входное сопротивление смесителя 1.5 kOm

11. Входная емкость смесителя 2.5 pF

12. Выходное сопротивление смесителя 330 Оm

13. Промежуточная частота 10.7MHz.

14. Входное сопротивление УПЧ 330 Оm

15. Выходное напряжение RSSI при входном уровне 35dB^VEMF....... 0.1-0.5V.

16. Выходное напряжение RSSI при входном уровне 65dBnVEMF...........0,95-1.45V

17. Выходное напряжение RSSI при входном уровне 100dBMVEMF ...... 1.9-2.7V

18. Выходное сопротивление выхода RSSI..........15 25 kOm

19. Уровень логического нуля выхода данных (DATA)............0,4V

20. Уровень логической единицы выхода данных (DATA) 0,9...1 от Vcc

21. Уровень логической единицы для управления по выводам 17 и 3 0,9...1 от Vcc

22. Уровень логического нуля для управления по выводам 17 и 3 не более 0,2V.

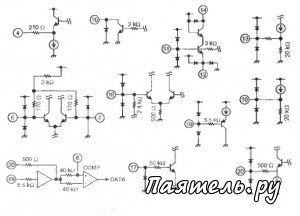

Эквивалентные схемы выводов: